- Project name

- Department

- Keyword

- Project

- Joint research

- Collaboration track record

- Profile

- Research introduction video

Development an innovative communication system with error-free POF

Building a distributed MEC environment for Beyond 5G

Department

Computer / Network / Parallel Distributed Processing / Real Time System

Keyword

Beyond 5G / codec / FPGA (Field-Programmable Gate Array) / ASIC (Application Specific Integrated Circuit) / AI application

Project

This research aims to eliminate the need for error correction functions and waveform shaping circuits in conventional communication systems by using error-free POF (Plastic Optical Fiber), thereby solving the problems of heat generation, delay, and cost in communication systems at once.

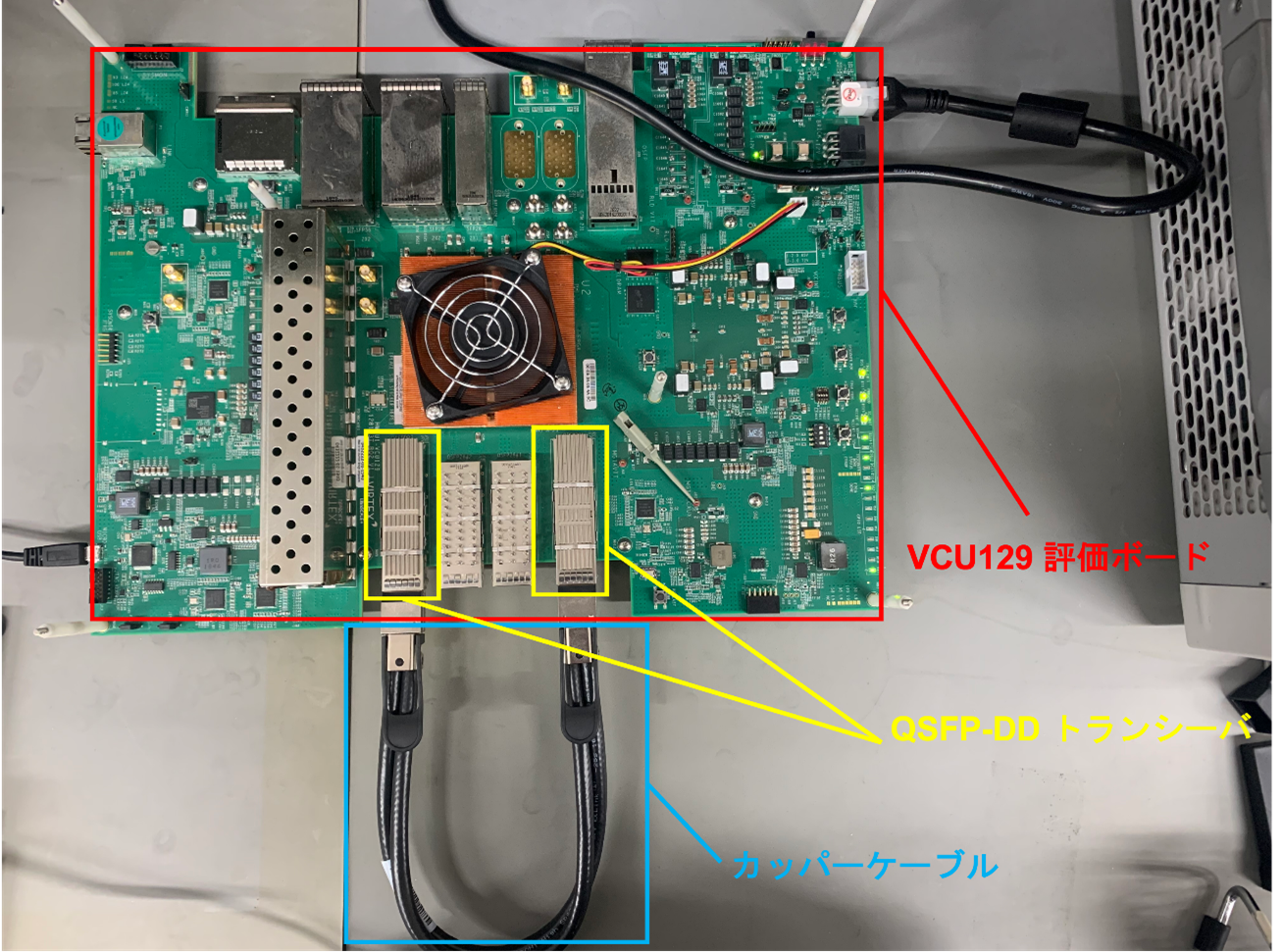

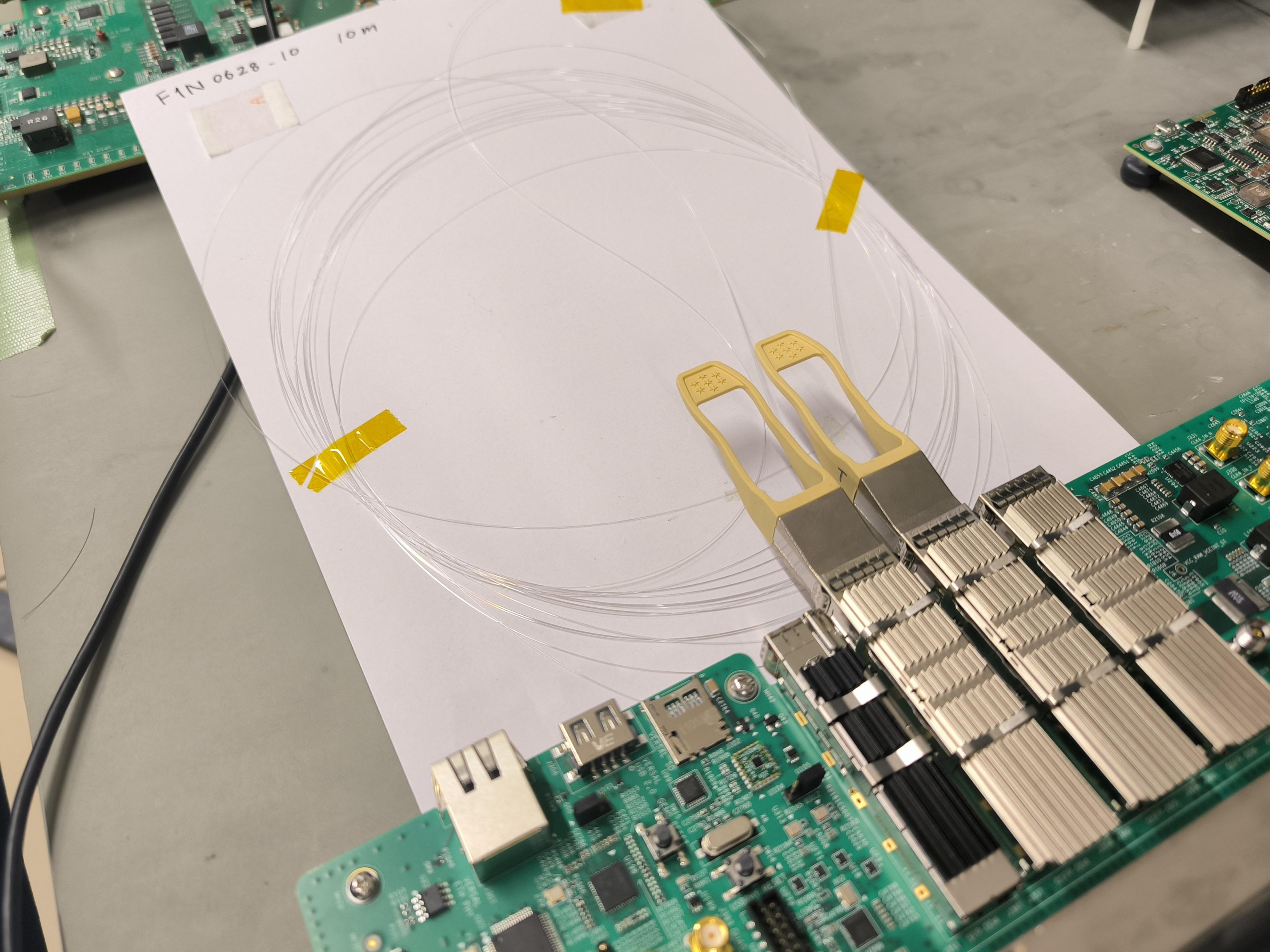

Error-free POFs released in the 2021 press release eliminate the need for error correction functions represented by Forward Error Correction (FEC), enabling new Beyond 5G systems that achieve low power consumption, low latency, and low cost. However, error-free POF transmission system technology without FEC is still underdeveloped and requires immediate problem solving. The ultimate goal of this research is to establish a communication technology that achieves 50 Gbps-class data transmission per lane without error correction using error-free POF (Plastic Optical Fiber) with a multi-level modulation scheme. Furthermore, we aim to establish a multi-core technology by batch molding error-free POF and compare its performance with that of existing error-correcting communication systems to demonstrate the superiority of error-free POF transmission systems in terms of reliability, transmission performance, power consumption, communication delay, and so on. Based on these goals, we are currently designing and verifying network chips for error-free POF as a distributed MEC (Multi-Access Edge Computing) environment for Beyond 5G. Specifically, we are designing and verifying network chips that can control error correction and detection for error-free POF verification, and verifying the reduction of power consumption and communication delay by error-free POF. The network chip can be selected between an Ethernet-compatible codec and a newly designed codec that maximizes the performance of error-free POF, and can be freely configured with or without error detection and correction functions to enable a variety of verifications. We are also developing prototypes of codecs for error-free POFs.

Desired joint research

- Processor for real-time processing

- Distributed controller

- Network-on-Chip architecture

Image

- I/O processing for spacecraft and robot control

- Real-time processing unit (context cache)

- Optical fiber

Collaboration track record

- Space Responsive Multithreaded Processor (SRMTP)

- Non-Volatile I/O Core

- Responsive Link

Profile

| Department: | Department of Information and Computer Science |

|---|---|

| Major: | School of Science for Open and Environmental Systems |

| Title: | Professor |

1996 Completed Doctoral program, Graduate School of Science and Technology, Keio University

1996-1998 Researcher, Electronics Research Institute, Industrial Technology Research Institute, Ministry of International Trade and Industry

1997-2000 Researcher, Sakigake Research 21, Japan Science and Technology Corporation

1998-2000 Research Assistant, Faculty of Science and Technology, Keio University

1998-2002 COE Research Fellow, Electrotechnical Laboratory

2000-2004 Full-time Lecturer, Faculty of Science and Technology, Keio University

2002- Visiting Researcher, Digital Human Research Center, National Institute of Advanced Industrial Science and Technology (AIST)

2004-2013 Associate Professor, Faculty of Science and Technology, Keio University

2013- Professor, Faculty of Science and Technology, Keio University